# GSM 900/DCS 1800 Fractional-N Frequency Synthesizer with Very Fast Settling Time

B. Neurauter <sup>1</sup>, G. Märzinger <sup>1</sup>, T. Lüftner <sup>3</sup>, R. Weigel <sup>1,3</sup>

M. Scholz <sup>2</sup>, V. Mutlu <sup>2</sup>, J. Fenk <sup>2</sup>

<sup>1</sup>Institute for Communications and Information Engineering, University of Linz, Austria

<sup>2</sup>Infineon Technologies, Munich, Germany

<sup>3</sup>DICE Danube Integrated Circuit Engineering, Linz, Austria

**Abstract -** This paper presents a programmable phase-locked-loop (PLL)-based fractional-N frequency synthesizer that uses a third-order  $\Delta\Sigma$ -modulator. The in-band phase noise of -97 dBc/Hz in the integer-mode and -94 dBc/Hz in the fractional-mode is measured at 30 kHz offset. In addition to offering an ultra-fine frequency resolution of down to 12.4 Hz and very low in-band phase noise this frequency synthesizer offers, with a loop-bandwidth of about 100 kHz, a very fast settling time of less than 95  $\mu$ s when a 75 MHz jump is applied. This feature enables multiple applications RF applications including GSM to send a signal and quickly reset to send another signal to meet high data throughput requirements.

## I. INTRODUCTION

In the last decade the field for low-cost universal frequency synthesizers has grown considerably. Frequency synthesizers based on an integer-N phase-locked-loop (PLL) often lead to problems in meeting various specifications due to their tradeoff between loop bandwidth and channel spacing. In every complex digital modulation scheme, as in the global system for mobile communications (GSM), the phase noise of the frequency synthesizer is a very critical parameter. When their specifications require a fine channel spacing, a lower comparison frequency must be used which leads to high division values with standard integer-N PLLs that directly degrades the phase noise performance. The problem of low comparison frequency can be avoided by using a delta-sigma

( $\Delta\Sigma$ ) modulated fractional-N PLL [1]. This technique and the use of a high comparison frequency lead to good levels of phase noise and reference frequency feedthrough suppression [2].

The demonstrator of our frequency synthesizer also offers a very low step size of 12.4 Hz when operated at a reference frequency of 13 MHz [3]. When applied to the GSM-system, where an accuracy of 0.1 ppm for the carrier of the transmitted signal is required, a digital correction method can be used instead of the currently used analog tuning of a voltage controlled temperature compensated crystal oscillator (VCTCXO).

Due to the fact that our ( $\Delta\Sigma$ ) modulated fractional-N PLL uses a high comparison frequency and a wide loop filter bandwidth, a fast switching speed can be achieved when changing the carrier frequency in a GSM handset.

## II. FRACTIONAL-N FREQUENCY SYNTHESIS TECHNIQUES

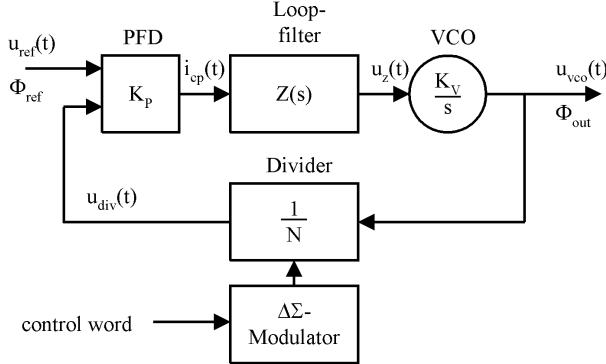

Indirect frequency synthesis based on a fractional-N phase locked loop as shown in Fig. 1 obtains a fine frequency resolution by interpolating a fractional division value using an oversampling ( $\Delta\Sigma$ ) modulator with a coarse frequency divider. This architecture offers the possibility to have a frequency resolution smaller than  $f_{ref}$ .

One easy way to control the actual divider value is to use the carry-out of an accumulator to toggle between two divider values N and N+1 of a dual modulus prescaler. The PLL lowpass characteristic may be

Figure 1: Frequency synthesizer with  $\Delta\Sigma$ -modulated fractional-N PLL

utilized to filter the divider values to get the required fractional division. The spectrum of the switching sequence has well defined spurious noise lines due to the short periodicity in the phase error signal. This spurious lines appear as well defined spurious tones in the spectrum of the output signal at multiples of the frequency offset.

Due to the fact that the phase error is easy to predict a compensating signal can be summed into the PLL to cancel this error. The complexity of this interpolation technique makes it unsuitable for many applications.

When ( $\Delta\Sigma$ ) modulators with higher order are used it is permitted to model the quantization noise as added white noise. Such modulators are also less susceptible to a constant input signal. This principle was first used in digital to analog conversion, where the ( $\Delta\Sigma$ ) modulator switches between coarse quantized voltage levels to get the desired output voltage.

### III. SYNTHESIZER IMPLEMENTATION

As shown in Fig. 1 we have implemented a high performance frequency synthesizer. The phase-frequency detector (PFD) is a conventional sequential structure with a tri-state charge pump followed by a single ended 5-element off-chip low pass filter [4]. The voltage controlled oscillator (VCO) is an external module with a tuning range to cover the GSM 900 and DCS 1800 transmit band. The value of the synthesized frequency is determined by the division factor in a new

multi-modulus structure which was also implemented in a custom IC. To control the divider values in the fractional-N frequency synthesizer a third order multi-stage noise shaping (MASH) structure with an eight-level quantizer is used. This quantizer expands the division range within (N-3) to (N+4).

### IV. NOISE TRANSFER FUNCTIONS

The closed-loop transfer function of Fig. 1 can be derived as

$$\frac{\Phi_{out}(s)}{\Phi_{ref}(s)} = N \frac{1}{1 + \frac{N}{K_P K_V} \frac{s}{Z(s)}} = NG(s) \quad (1)$$

where  $N$  is the divider value,  $K_P$  [A/rad] and  $K_V$  [rad/Vs] are the conversion gain values of the PFD and the VCO respectively;  $Z(s)$  [ $\Omega$ ] is the Laplace transform of the transimpedance of the loop filter and  $s$  is the complex Laplace variable.

Based on the linear white noise model that is valid for  $\Delta\Sigma$  modulators for second and higher order the phase noise  $S_{\Phi,n,m}$  added by the  $\Delta\Sigma$  modulator is given by

$$S_{\Phi,n,m}(f) = \frac{(2\pi)^2}{12F_{ref}} \left[ 2 \sin \left( \pi \frac{f}{F_{ref}} \right) \right]^{2(m-1)} \frac{\text{rad}^2}{\text{Hz}} \quad (2)$$

where  $m$  represents the order of the modulator.

With the use of the linear model of a fractional-N PLL this phase noise will be low-pass filtered to the output with the transfer function  $G(s)$ . Then the power density at the output of the VCO can be approximated by the following expression:

$$S_{\Phi,n,pll}(f) = S_{\Phi,n,m}(f) |NG(j2\pi f)|^2 \quad (3)$$

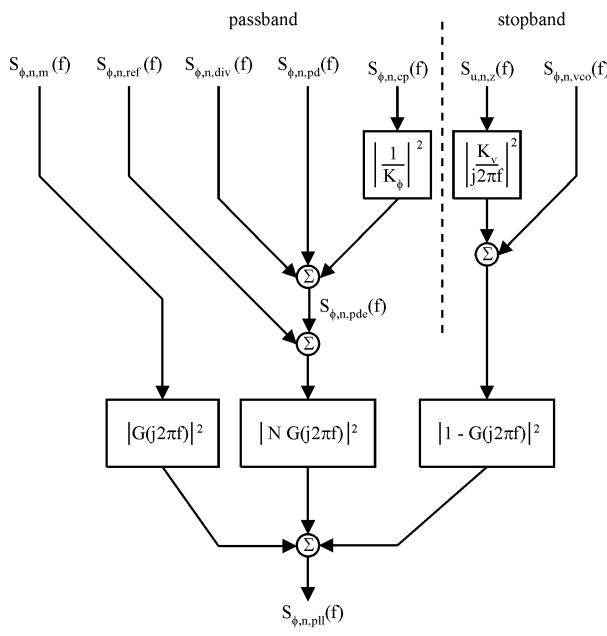

For a complete noise analysis of a  $\Delta\Sigma$  modulated fractional-N PLL the model proposed in Fig. 2 has to be used [5]. The noise sources in the PLL design added from each block are:

- $S_{\Phi,n,PD}$  ... Phase noise due to the phase frequency detector

- $S_{\Phi,n,ref}$  ... Phase noise of the reference oscillator

- $S_{\Phi,n,div}$  ... Phase noise due to the divider

- $S_{\Phi,n,CP}$  ... Noise in charge pump current

- $S_{u,n,z}$  ... Thermal noise generated by the loop filter resistors

- $S_{\Phi,n,m}$  ... Phase noise due to the MASH-modulator

- $S_{\Phi,n,VCO}$  ... Phase noise due to the VCO

Figure 2: Noise model for  $\Delta\Sigma$  modulated fractional-N PLL

When all the individual noise sources are filtered with the appropriate transfer function the total phase noise at the output of the VCO is given by:

$$\begin{aligned}

S_{\phi,n,pll}(f) = & \{S_{\phi,n,m}(f) + N^2[S_{\phi,n,ref}(f) + \\

& S_{\phi,n,pde}(f)]\} |G(j2\pi f)|^2 \\

& + \{S_{\phi,n,vco}(f) + S_{u,n,z}(f)\} \left| \frac{K_v}{j2\pi f} \right|^2 \\

& |1 - G(j2\pi f)|^2

\end{aligned} \quad (4)$$

## V. CIRCUIT REALIZATION AND MEASUREMENT RESULTS

A prototype synthesizer was fabricated in a 25 GHz BiCMOS process with  $0.6 \mu\text{m}$  minimum feature size containing the PFD, charge pump and multi-modulus divider. The third order MASH  $\Delta\Sigma$ -modulator and the additional control logic are implemented in a field programmable gate array (FPGA).

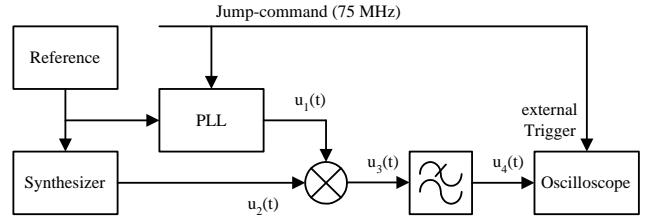

As mentioned before, our  $\Delta\Sigma$  modulated fractional-N PLL uses a high comparison frequency and a wide loop filter bandwidth. This enables a fast switching speed when changing the output frequency. The measurement setup shown in Fig. 3, where a passive mixer performs the operation of a phase detector, is used to measure the switching time of our implemented  $\Delta\Sigma$  modulated fractional-N frequency synthesizer.

Figure 3: PLL lock-in time measurement setup

The output voltage  $u_4(t)$  (Fig. 3) can be expressed by the following equation:

$$u_4(t) = \frac{U_{1,0}U_{2,0}}{2} \sin[\Phi_e(t)] \quad (5)$$

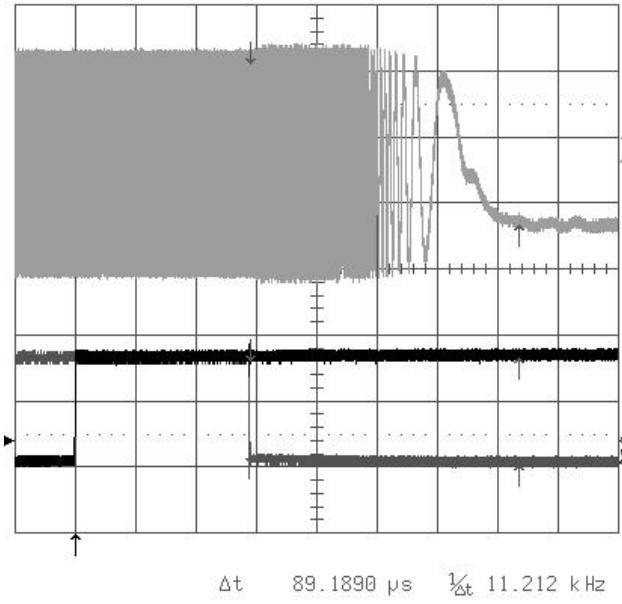

In a GSM-transmitter the settling requirements for the synthesizer are defined by:

$$|\Phi_e(t) - \Phi_e(t \rightarrow \infty)| < 5^\circ \quad (6)$$

Simulations for a 75 MHz jump from 1710 MHz to 1785 MHz predict a settling time of approximately 95  $\mu\text{s}$ .

Measurements, as shown in Fig. 4, demonstrate that the implemented frequency synthesizer operates with a settling time of smaller than 95  $\mu\text{s}$  when changing the output frequency from 1710 MHz to 1785 MHz.

State of the art fractional-N frequency synthesizers for GSM- and GPRS-applications as presented in [6] perform such a frequency change in about 180  $\mu\text{s}$ .

Figure 4: PLL lock-in time measurement result

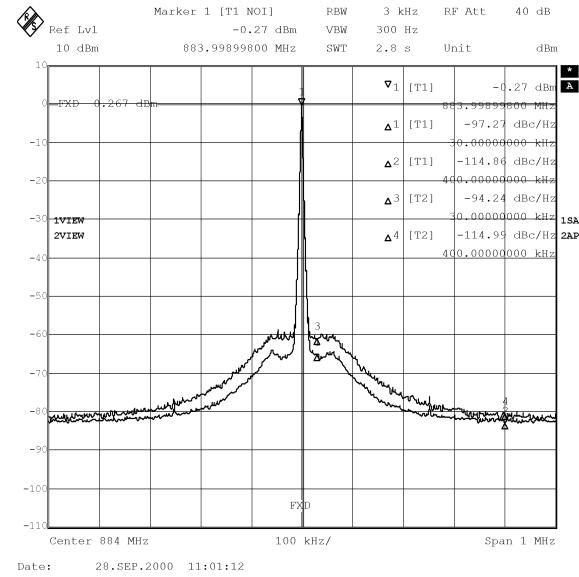

The measurement results shown in Fig. 5 demonstrate the good phase noise performance of the prototype synthesizer. Here the output of the VCO was set to a fractional frequency of  $F_{out}=884.2$  MHz and an integer frequency of  $F_{out}=884$  MHz.

## VI. CONCLUSION

A programmable PLL-based fractional-N frequency synthesizer that uses a third-order  $\Delta\Sigma$ -modulator with inband phase noise of up to -97 dBc/Hz at 30 kHz offset is presented. This synthesizer offers an ultra-fine frequency resolution of down to 12.4 Hz and a very fast settling time of less than 95  $\mu$ s when a 75 MHz jump is applied. The proposed system meets the requirements of many RF applications including GSM.

## REFERENCES

[1] B. Miller, J. Conley, "A Multiple Modulator Fractional Divider", *IEEE Transactions on Instrumentation and Measurement*, Vol. 40, No. 3, June 1991, pp. 578-583

Figure 5: Measured spectrum at  $F_{out} = 884.2$  MHz and  $F_{out} = 884$  MHz

- [2] W. Rhee, B.-S. Song, "A. Ali, A 1.1-GHz CMOS Fractional-N Frequency Synthesizer with a 3-b Third-Order  $\Delta\Sigma$  Modulator", *IEEE Journal of Solid State Circuits*, Vol. 35, No. 10, October 2000, pp. 1453-1460

- [3] B. Neurauter, G. Märzinger, T. Lüftner, R. Weigel, M. Scholz, V. Mutlu, J. Fenk, "Low Phase Noise Frequency-Synthesizer with Very High Frequency-Resolution for GSM 900/DCS 1800", *Proc. European Microwave 2000*, October 2000, pp. 124-127

- [4] J. L. Stensby, *Phase-Locked-Loops: Theory and Applications*, CRC Press LLC 1997

- [5] V. F. Kroupa, "Noise Properties of PLL Systems", *IEEE Transactions on Communications*, Vol. 30, No. 10, October 1982, pp. 2244-2252

- [6] C. Wuensch, "Fractional-N Synthesizers Meet HSCSD And GPRS Demands", *Microwave & RF*, August 1999, pp. 105-121